搜索到2條【沉積和刻蝕技術(shù)】相關(guān)的全部。

搜索到2條【沉積和刻蝕技術(shù)】相關(guān)的全部。

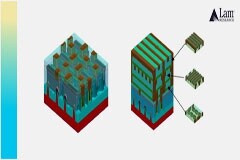

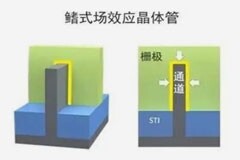

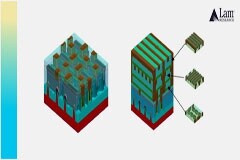

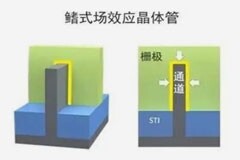

3D時(shí)代值得關(guān)注的趨勢(shì)

3D NAND GAA晶體管 存儲(chǔ)器 (DRAM) 2023-6-2 13:30

3D NAND GAA晶體管 存儲(chǔ)器 (DRAM) 2023-6-2 13:30

加載更多

查看關(guān)鍵詞的分類頻道

查看關(guān)鍵詞的分類頻道

搜索到2條【沉積和刻蝕技術(shù)】相關(guān)的全部。

搜索到2條【沉積和刻蝕技術(shù)】相關(guān)的全部。

3D NAND GAA晶體管 存儲(chǔ)器 (DRAM) 2023-6-2 13:30

3D NAND GAA晶體管 存儲(chǔ)器 (DRAM) 2023-6-2 13:30

查看關(guān)鍵詞的分類頻道

查看關(guān)鍵詞的分類頻道